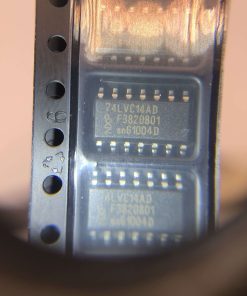

Description

Feature

JEDEC DDR2 Compliant

– Double-data rate on DQs, DQS,DM bus – 4n Prefetch Architecture

Throughput of valid Commands

– Posted CAS and Additive Latency(AL) Signal Integrity

– Configurable DS for system compatibility – Configurable On-Die Termination

-Auto Refresh and Self Refresh Modes Power Saving Modes – Power Down Mode

– Partial Array Self Refresh(PASR)

SSTL_18 compliance and Power Supply -VDD/VDDQ=1.70 to 1.90V